基于ZYNQ,的通用算法半实物验证平台*

时间:2023-02-16 13:05:08 来源:千叶帆 本文已影响人

张智维,陈鑫,陈凯,张颖,刘涛,王雷

(南京航空航天大学电子信息工程学院,江苏 南京 211106)

传统的算法验证平台主要是基于中央处理器(Central Processing Unit,CPU)、图形处理器(Graphics Processing Unit,GPU)、专用集成电路(Application Specific Integrated Circuit,ASIC)和现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)等实现。CPU 通用性强,但串行运算的特点使其在数字信号处理领域受限[1]。GPU 在一定程度上弥补了CPU 的缺点,但其本质上仍然是指令流驱动的处理器,特别是成本和功耗居高不下[2],对开发者并不友好。ASIC性能优越、保密性强,被广泛应用于数字信号处理领域,但其灵活性低[3],算法任何细微的变动都有可能导致开发者需要重新设计芯片电路。FPGA 可编程和全并行运算的特点使得其在数字信号处理领域受到青睐[4],但其也存在开发周期过长的缺点。

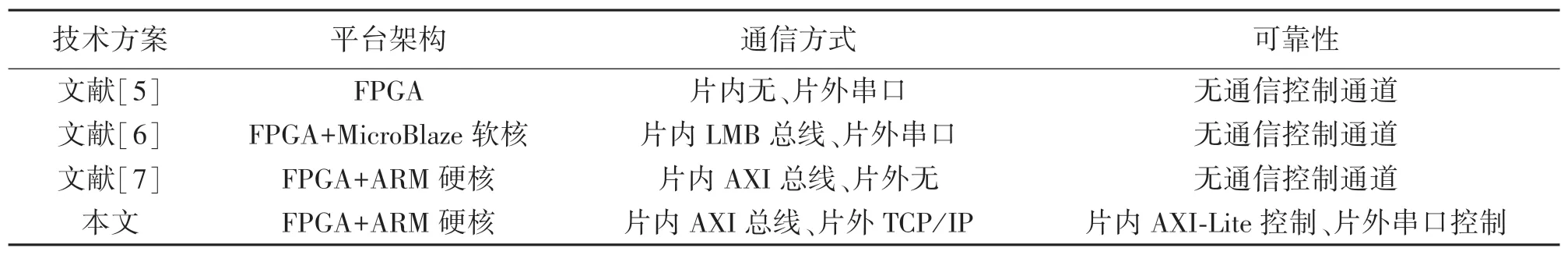

文献[5]基于FPGA 搭建了一个通用的画质处理算法平台,该平台利用FPGA 资源运行算法并通过串口和上位机进行数据交换,其纯FPGA 的硬件架构导致其算法平台控制能力弱且串口通信方式较慢。文献[6]基于FPGA 和MicroBlaze 软核搭建了一个图像处理平台,其中MicroBlaze 是在FPGA 内部实现的具备CPU 功能的软核,其性能弱于硬核CPU 且该平台串口的通信方式较慢。文献[7]利用FPGA 和CPU 硬核搭建了一个实时视频图像处理平台,该平台在FPGA 端完成图像处理算法,并通过片内总线完成FPGA 和CPU 的数据交换。但其片内通信中没有额外的控制通道,使得其通信稳定性受到考验,且其尚未实现平台和上位机的通信接口。

ZYNQ 芯片内部包含ARM 处理系统(Processing System,PS) 和可编程逻辑(Programmable Logic,PL)[8-9],并且片内的AXI 通信总线可用于PL 和PS之间高速双向传输数据[10-13]。基于上述优点,ZYNQ 被研究人员广泛应用在各种电子系统设计中。文献[14]中的接收机平台利用PL 端的硬件逻辑资源处理射频前端信号以及利用PS 端完成数据分析,文献[15]中的高速数据采集系统利用挂载在PL 端的传感器完成数据采集以及PS 端完成数据存储和显示,文献[16]中的千兆以太网数据包处理架构在PL 端搭建硬件逻辑以及利用PS 端完成软件处理工作,文献[17]中的视频处理系统利用PL 端完成图像预处理以及PS 端完成图像识别算法,文献[18]基于Linux 操作系统在ZYNQ 中实现了一个FC 交换机平台。上述设计都是针对特定场景的专用系统,可移植性差,无法被用于不同的应用场景。

由于ZYNQ 的硬件结构同时包含PS 和PL 模块,特别适合进行包含软件和硬件开发的系统设计,因此,本文围绕ZYNQ 芯片建立了一个通用算法半实物验证平台。该平台主要包含可编程逻辑(PL),ARM 处理系统(PS)、上位机,以及对应的接口模块,所有功能均采用模块化的设计思想,只需对其做很小的改动就可以移植到不同的算法应用场景中,能够满足绝大部分算法验证的需求。与此同时,本文作者在研究过程中发现,PL 和PS 之间虽然可以依靠直接存储器访问(Direct Memory Access,DMA)进行高速通信,但其可靠性较差。为此,本平台基于AXI-Lite 总线通信接口,在PL 和PS 之间设计双向握手协议。此外,当PS 运行在裸机模式时,PS 和上位机之间的TCP/IP 通信模块必须独占CPU 运行时间,否则会丢失通信链路。为保证PS 和上位机之间可以长时间稳定交换数据,本平台设计了由串口控制的TCP/IP 通信模块。实验结果表明,该验证平台工作稳定可靠,该平台的上行和下行数据传输速率分别达到144 Mbit/s和133 Mbit/s,上述特点使得该平台可适用于图像处理等运算复杂的应用领域。

平台架构如图1 所示,PL、PS 和上位机三部分构成。PL 提供FPGA 资源,可以实现复杂运算的高速执行和接口扩展。PS 是一个包含ARM CPU 的SOC 系统,具有丰富的外部接口,并且是基于C 语言编程,可以作为系统的控制模块,以及快速算法实现。上位机的功能则是激励数据的下放,以及对上行数据进行分析处理和存储。

图1 平台架构图

如图1 所示,为保证数据传输可靠稳定,本平台以AXI-Lite 和串口作为控制通道。AXI-Lite 是ZYNQ 片内32 位轻量级数据总线,PL 和PS 通过该总线读写特定地址的寄存器便可控制数据的传输。串口是PS 和上位机之间的控制通道,PS 可通过串口向上位机输出控制信息以及上位机可通过串口输入控制指令。

数据上行时,PL 端运算模块输出的原始数据经过转换模块转换后被送入发送FIFO 中。随后AXIDMA 通道直接把数据从发送FIFO 取出送入PS 端的DDR3 中存储。PS 再把数据从DDR3 中取出通过TCP/IP 模块把数据发送给上位机。

数据下行时,上位机通过TCP/IP 模块把数据发送给PS 端的DDR3 中存储,随后数据通过AXIDMA 通道直接被送到PL 端的接收FIFO 中。接收FIFO 把数据送入转换模块,转换后数据被发送给运算模块。

为保证PL 和PS 之间的DMA 传输通道稳定可靠,本平台基于AXI-Lite 设置双向握手协议。数据上行架构如图2(a)所示,数据从PL 端的发送FIFO通过DMA 通道直接送到PS 端的DDR3 中。数据上行时的握手协议靠PS 控制ACK 变量、寄存器2 和寄存器1 以及PL 控制寄存器1 和寄存器2。数据下行架构如图2(b)所示,数据从PS 端的DDR3 通过DMA 通道直接送到PL 端的接收FIFO 中。数据下行时的握手协议靠PS 控制SEND 变量、寄存器2以及PL 控制寄存器2。

图2 PL 和PS 数据交换架构图

数据从PL 到PS 的操作流程如图3 所示。PS通过AXI-Lite 总线拉高寄存器2 的请求信号并将ACK 变量置0。PL 监测到请求信号的上升沿后把寄存器1 的值置0,并启动一次DMA 发送。DMA 每发送完一次,PL 都通过AXI-Lite 总线把寄存器1 的值累加1 并和预设值比较。如果寄存器1 的值小于预设值,则PL 需要继续启动一次DMA 发送;

如果寄存器1 的值大于预设值则表明PL 发送数据完毕。在PL 发送数据期间,PS 会通过AXI-Lite 总线不断读寄存器1 的值并和ACK 变量比较。如果ACK 值小于寄存器1 的值则证明PL 发送了新的尚未被PS 接收的数据,即PS 需要启动一次DMA 接收。因为PL 端运行频率是100 MHz,PS 端运行频率是666 MHz 且PL 和PS 是相互独立运行,这就意味着PL 写数据比PS 读数据慢。因此,当ACK 值不小于寄存器1 的值但不大于预设值时则证明PL正在发新的数据,此时PS 需要循环等待且需要一直监测判断。当ACK 值不小于预设值时则证明所有数据都被PS 接收完毕,PS 立即拉低请求信号。

图3 数据从PL 到PS 的操作流程

数据从PS 到PL 的流程如图4 所示。PS 拉高发送信号并将SEND 变量置0,随后延时启动一次DMA 发送并将SEND 变量加1。如果SEND 变量小于预设值则PS 继续发送数据;

如果SEND 变量不小于预设值则证明发送数据完成,PS 延时拉低发送信号。当PL 监测到PS 拉高发送信号后,就保持接收FIFO 的读信号一直有效且不断把接收FIFO 中的数据存储。当PL 检测到发送信号下降沿后,则证明数据全部接收完毕。由于PS 运行频率更高,所以PS 写数据比PL 读数据更快。为防止PL 来不及读PS 发送的数据则PS 在每启动一次DMA 发送之前都需要做延时处理以确保数据能被PL 读。同时,PL 需要保证读信号一直有效。当PS 发送完所有数据后,不能立即拉低发送信号,需要延时以确保PL读完所有数据。通过延时策略,PS 发送数据时的握手协议被简化。

图4 数据从PS 到PL 的操作流程

本平台利用TCP/IP 模块实现和上位机稳定交换数据,考虑到应将ZYNQ 作为通信的主动方,所以把ZYNQ 作为服务器使用。当上位机需要通信时便通过串口通知ZYNQ 启动TCP 服务器。因为裸机服务器在启动后就需要进入无限循环,但由于本平台有其他功能模块,所以不能使服务器模块一直处于运行状态,所以只有当外部设备需要服务器时才会重新配置并开启。由TCP/IP 协议可知,在同一平台中多次配置服务器则必须保证服务器的IP 地址和端口不能完全相同,所以本平台固定IP 地址,每一次配置服务器时将端口号逐步递增,端口信息会在服务器准备就绪后通过串口输出。

PS 和上位机交换数据的流程如图5 所示。上位机通过串口向PS 输入控制指令,PS 启动TCP 服务器并通过串口输出TCP 服务器的端口号和IP 地址,然后等待上位机连接。完成数据交换后便关闭TCP 服务器。

图5 PS 和上位机数据交换流程

基于上述算法平台,设计了一个摄像头图像实时传输显示平台。综合PL 端的逻辑资源和运行频率,本显示平台将发送FIFO 的宽度设置为16位、深度为16K,接收FIFO 的宽度设置为16 位、深度为8K。PL 端被替换成如图6 所示,摄像头和显示器分别作为采集终端和显示终端。摄像头将实时采集到图像数据经过转换后送入发送FIFO 中随后数据通过AXI-DMA 通道被传输至PS。图像数据被PS 处理后紧接着被传回至PL 端的接收FIFO 中,PL 端把接收FIFO 中的数据取出转换后存入RAM,HDMI 模块则从RAM 中读出图像数据并送入显示器显示。经过测试,PL 到PS 的数据传输速率可达144 Mbit/s,PS 到PL 的数据传输速率可达133 Mbit/s。

图6 图像传输实时显示平台中PL 端架构图

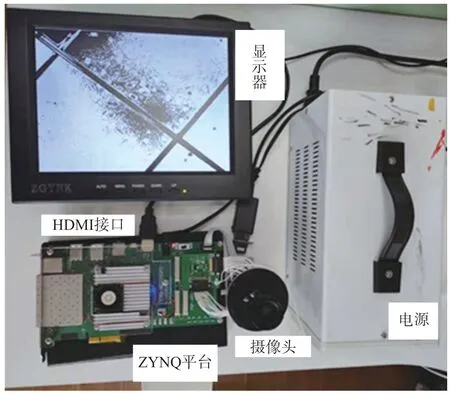

本文基于ZYNQ-SOC 设计了一个通用的半实物算法验证平台。平台实物如图7 所示。模块化的系统架构使得平台可移植性高。实验结果表明,通过握手协议,该平台传输数据高速且稳定可靠,片内传输数据双向均达130 Mbit/s,片外TCP/IP 传输速度达50 Mbit/s。可适用于复杂算法领域的验证工作。如表1 所示,对比文献[5-6],本文采用的FPGA+ARM 硬核的硬件架构使得平台的性能更强大,同时片内采用的AXI 通信总线传输数据更快,串口控制的TCP/IP 通信方式比串口通信更稳定、高效。和文献[7]相比,本文在实现片内通信的基础上加入控制通道,使得片内通信更稳定。同时,本文实现了平台和外部通信的TCP/IP 接口。

图7 图像实时传输显示平台实物

表1 不同算法验证平台技术方案对比

猜你喜欢 寄存器上位串口 一场史无前例的乐队真人秀智族GQ(2019年9期)2019-10-28飞思卡尔单片机脉宽调制模块用法研究科技创新与应用(2018年23期)2018-09-13移位寄存器及算术运算应用电子技术与软件工程(2018年1期)2018-03-22MCS—51单片机中的多串口通讯技术的应用电子技术与软件工程(2017年5期)2017-04-23数字电路环境下汽车控制电路信号设计科教导刊·电子版(2016年36期)2017-04-22基础油“上位”汽车观察(2015年10期)2016-04-06全国计算机等级考试机房准备工作探讨电脑知识与技术(2014年11期)2014-06-18微机串口的测试诊断中国信息化·学术版(2013年5期)2013-10-09基于VC的PLC数据采集管理系统现代电子技术(2009年6期)2009-05-31基于VC串口通信的实现智能计算机与应用(2007年3期)2007-07-05 相关热词搜索:算法,实物,验证,